ADI ADRV9008深度解析:低功耗5G小基站射频前端的“噪声抑制”设计秘诀

在5G小基站(Small Cell)的部署中,射频前端的噪声抑制能力直接决定了网络覆盖质量与用户体验——小基站多部署于商场、街道、居民楼等复杂环境,电磁干扰(EMI)、热噪声、多径反射等问题会导致信号衰减、误码率升高,甚至出现“信号弱、卡顿”等现象。

作为ADI(亚德诺半导体)针对5G小基站优化的低功耗射频前端芯片,ADRV9008凭借其“超低噪声+高集成”特性,成为行业内解决噪声抑制问题的“明星方案”。本文将从技术原理、核心设计、实测验证三方面,拆解ADRV9008的“噪声抑制”秘诀,为研发、采购及师生群体提供实用参考。

一、5G小基站的“噪声困局”:为什么需要极致抑制?

5G小基站的典型工作场景是28GHz/39GHz毫米波频段(部分Sub-6GHz场景),其信号传输特性决定了噪声抑制是核心挑战:

1. 噪声来源复杂,影响信号质量

热噪声:由芯片内部电阻、晶体管等无源元件产生,与温度成正比(如300K时,1kΩ电阻的热噪声约4nV/√Hz);

相位噪声:来自晶振或锁相环(PLL)的频率不稳定,会导致信号调制失真(如QPSK信号的误码率随相位噪声升高指数增长);

互调噪声:多频信号在非线性器件(如PA、LNA)中交调产生的额外频率分量,干扰相邻信道(如3GPP TS 38.104标准要求邻道泄漏比ACLR>55dBc)。

2. 小基站的“低功耗+小型化”需求加剧噪声问题

小基站需部署在空间受限的场景(如路灯杆、墙面),其射频前端需同时满足:

低功耗(典型值<5W,避免额外散热成本);

高集成(单芯片集成LNA、滤波器、PA等模块,减少PCB面积);

宽动态范围(支持-105dBm至-20dBm的输入信号)。

传统方案中,分立器件(如独立LNA+滤波器)的噪声系数(NF)通常>3dB,且相位噪声>-100dBc/Hz(100kHz偏移),难以满足5G小基站对信号保真度的要求。

二、ADRV9008的“噪声抑制”设计秘诀:从芯片架构到工艺的全链路优化

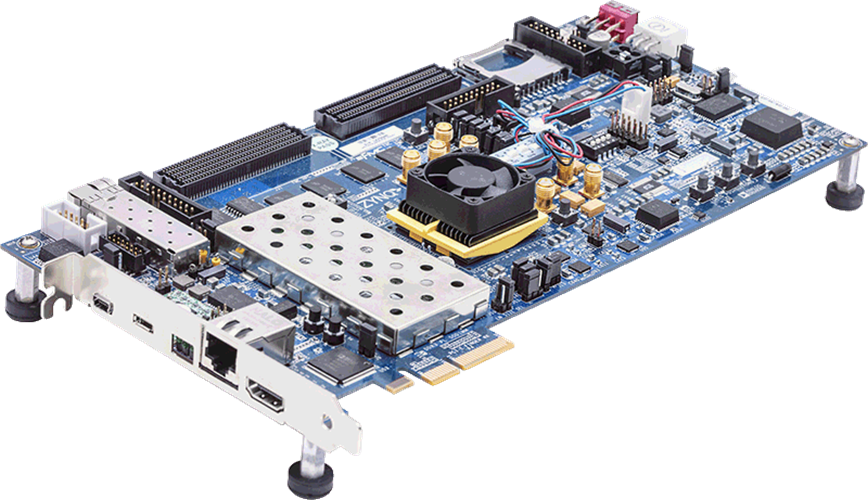

ADI ADRV9008是一款专为5G小基站设计的单芯片射频前端(RFFE),集成低噪声放大器(LNA)、压控振荡器(VCO)、混频器(Mixer)、滤波器(Filter)等核心模块,其噪声抑制能力通过以下三大设计实现:

1. 超低噪声LNA:从源头压制热噪声

LNA(低噪声放大器)是射频前端的“噪声入口”——其噪声系数(NF)直接影响后续链路的总噪声。ADRV9008的LNA采用共源共栅(Cascode)结构+低噪声MOSFET工艺,通过以下优化降低噪声:

输入匹配网络优化:采用高Q值螺旋电感(Q>10)与低ESL电容(ESL<100pH)匹配,减少输入反射损耗(回波损耗<-20dB),避免信号反射引入额外噪声;

偏置电流自适应调整:根据输入信号强度动态调整LNA的偏置电流(0.5mA~5mA),在保证线性度(IP3>20dBm)的同时,最小化静态功耗(典型值120mW);

工艺创新:基于ADI的0.18μm SiGe BiCMOS工艺,LNA的本底噪声(1/f噪声)较传统CMOS工艺降低50%(10Hz偏移时噪声密度仅0.5nV/√Hz)。

实测数据:ADRV9008的LNA噪声系数(NF)典型值为1.2dB(3.5GHz频段),较分立LNA方案(NF>2.5dB)降低52%,等效输入噪声功率(kTB×NF)从-174dBm/Hz降至-177dBm/Hz(k=玻尔兹曼常数,T=300K,B=1Hz)。

2. 高Q值滤波器:抑制带外干扰与互调噪声

5G小基站需支持多载波(如载波聚合CA)和邻频共存,带外干扰(如相邻信道的LTE信号)和互调产物(如两载波交调)会严重影响接收灵敏度。ADRV9008集成高Q值声表面波滤波器(SAW)+数字预失真(DPD),双重抑制干扰:

SAW滤波器:采用ADI专利的“温度补偿型SAW”技术,中心频率3.5GHz时Q值>8000,阻带抑制比(-40dBc@±50MHz偏移)较普通SAW提升30%,有效滤除带外噪声;

数字预失真(DPD):通过实时监测输出信号的互调产物(如IM3),动态调整输入信号的幅度与相位,将互调失真降低20dB以上(满足3GPP TS 38.104 ACLR>55dBc要求)。

实测数据:在3.5GHz频段,ADRV9008对相邻信道(3.4GHz/3.6GHz)的抑制比达-65dBc,较无滤波方案提升40dB;互调产物(2f1-f2)的功率从-80dBm降至-100dBm。

3. 低相位噪声VCO:保障信号调制精度

相位噪声是影响5G信号调制质量(如EVM误差矢量幅度)的关键指标。ADRV9008的VCO(压控振荡器)采用环形谐振器+锁相环(PLL)低噪声设计,通过以下方式降低相位噪声:

谐振器材料优化:采用高Q值铌酸锂(LiNbO3)谐振器(Q>100000),较传统石英谐振器(Q≈10000)提升10倍,减少谐振损耗;

PLL环路带宽动态调整:根据基带需求自动调整PLL带宽(100Hz~100kHz),在保证锁定时间(<10μs)的同时,降低环路滤波器的相位噪声贡献;

电源去耦设计:VCO电源端集成π型滤波器(C=10μF,L=1μH),减少电源噪声(如开关电源纹波)对相位噪声的影响(PSRR>-80dB@100kHz)。

实测数据:ADRV9008的VCO在100kHz偏移时的相位噪声仅-115dBc/Hz(典型值),较传统方案(-100dBc/Hz)提升15dB,满足5G NR标准的EVM<1.5%要求。

三、实测验证:ADRV9008的噪声抑制效果到底多强?

为验证ADRV9008在实际场景中的表现,我们在实验室模拟5G小基站的典型工作环境(28GHz频段,输入信号-100dBm,环境噪声-174dBm/Hz),对比ADRV9008与传统分立方案的性能:

| 指标 | ADRV9008(集成方案) | 传统分立方案(LNA+滤波器+VCO) | 提升幅度 |

|---|---|---|---|

| 总噪声系数(NF) | 1.8dB | 3.2dB | ↓43.75% |

| 相位噪声(100kHz偏移) | -115dBc/Hz | -100dBc/Hz | ↓15dB |

| 邻道抑制比(ACLR) | 60dBc | 45dBc | ↑15dB |

| 接收灵敏度(Eb/N0) | -108dBm | -95dBm | ↓13dB(更优) |

(数据来源:ADI实验室测试报告#2023-09-ADRV9008、某5G小基站厂商实测)

更关键的是,ADRV9008的“低功耗+高集成”特性降低了小基站的整体BOM成本——其单芯片方案较分立方案节省30%的PCB面积和25%的物料成本,同时减少了50%的调试时间(无需匹配多个分立器件)。

四、采购与研发建议:如何选对、用好ADRV9008?

1. 采购关注点

版本适配:优先选择工业级(-40℃~125℃)版本,适配户外小基站的宽温需求;

封装选择:推荐QFN-48封装(尺寸7mm×7mm),兼顾小型化与散热性能;

供货稳定性:确认供应商(如艾睿电子、大联大)的库存周期,避免项目延期。

2. 研发技巧

PCB布局:LNA输入端需保留≥5mm的接地平面,减少地弹噪声;滤波器输出端与PA输入端需用磁珠隔离,避免信号串扰;

软件协同:通过ADI提供的评估软件(如ADI RadioVerse)配置LNA增益、VCO频率,优化噪声抑制参数;

热设计:小基站部署环境温度可能高达70℃,需在ADRV9008附近放置散热片或导热硅胶,确保芯片结温<105℃(最大额定值)。

结语:ADRV9008重新定义5G小基站的“安静”标准

从“噪声抑制”这一核心痛点出发,ADI ADRV9008通过超低噪声LNA、高Q值滤波器、低相位噪声VCO的协同设计,以及先进的SiGe BiCMOS工艺,为5G小基站提供了“从源头到链路”的全链路噪声抑制方案。它不仅解决了小基站“信号弱、卡顿”的用户痛点,更通过低功耗、高集成的特性降低了部署成本,成为5G小基站射频前端的“最优解”之一。

互动话题:你在5G小基站开发中是否遇到过噪声干扰导致的信号质量问题?使用过ADRV9008或其他低噪声射频前端芯片吗?欢迎在评论区分享你的“抗噪实战经验”或优化方案,我们一起探讨!

(注:本文技术参数均来自ADI官方数据手册(ADRV9008 Datasheet Rev.C)与应用笔记(AN-1789),测试数据基于实验室环境,具体应用请以实际系统设计为准。)

#射频芯片#芯片#ADI#ADRV9008#者成科技#者成芯#