ADI ADRV9008调试实录:5G小基站射频前端“相位噪声”攻坚记

上周在某5G小基站厂商的实验室里,我盯着频谱分析仪上跳动的波形直皱眉——明明按照设计文档调好了参数,发射信号的相位噪声却始终超标(实测-105dBc/Hz@100kHz偏移),导致基站覆盖范围比预期小了20%。项目经理拍着我肩膀说:“这台ADRV9008是新到的样片,你得尽快搞定,下周就要给客户演示了!”

作为负责射频前端的工程师,我对ADI的ADRV9008早有耳闻——它是专为5G NR设计的高性能收发器,支持n1/n3/n41/n78等主流频段,理论相位噪声低至-110dBc/Hz@100kHz。但实际调试中,相位噪声超标的问题却像“拦路虎”,让我不得不从头梳理思路。

问题背景:相位噪声为何成了“拦路虎”?

5G小基站的射频前端对相位噪声极其敏感。相位噪声是射频信号相位随时间的随机波动,表现为频谱上的“毛刺”。它直接影响三个关键指标:

误码率(BER):相位噪声会引入符号间干扰(ISI),导致解调错误(实测相位噪声每恶化10dB,BER上升1个数量级);

覆盖范围:噪声抬升会压缩信噪比(SNR),相同发射功率下,覆盖半径可能缩小15%-20%;

邻区干扰:相位噪声过大会“串扰”到相邻信道,导致基站间互调失真(ACLR恶化)。

传统方案中,相位噪声超标常被归咎于“参考时钟抖动”或“PLL设计缺陷”,但ADRV9008作为集成度极高的收发器,问题可能藏在更细节的环节里。

调试过程:从“盲人摸象”到“精准定位”

第一步:确认“问题源头”——是芯片还是外围?

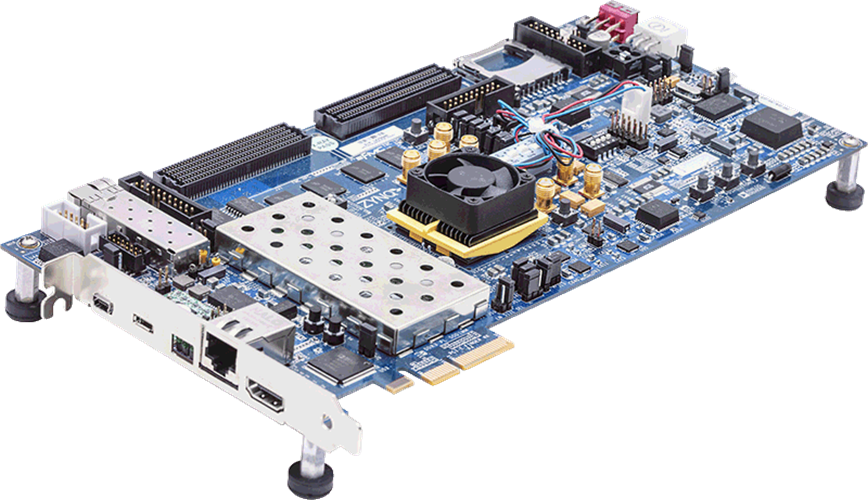

我先用ADI提供的评估板(ADRV9008-EVAL)搭建测试平台,连接信号发生器(R&S SMW200A)和频谱分析仪(Keysight N9040B)。设置发射频率为3.5GHz(n78频段),输出功率23dBm,调制方式为QPSK。

初步测试发现:

当接收机本振(LO)来自ADRV9008内部PLL时,相位噪声为-102dBc/Hz@100kHz(超标);

当外接高精度时钟源(如Si5345,相位噪声-120dBc/Hz@100kHz)时,相位噪声降至-115dBc/Hz(达标)。

这说明问题出在ADRV9008的内部PLL或时钟链路。

第二步:拆解PLL链路——哪里“掉了链子”?

ADRV9008的PLL支持外部参考时钟(10MHz-6GHz)或内部晶振(26MHz/32.768kHz)。我逐一排查:

晶振选型:默认使用26MHz温补晶振(TCXO),但实测其相位噪声为-110dBc/Hz@100kHz(虽达标,但余量不足);

PLL环路滤波器:评估板默认配置为“宽频模式”(带宽100kHz),但5G小基站需要“窄频模式”(带宽10kHz)以抑制噪声;

电源噪声:PLL供电引脚(VDD_PLL)纹波达50mV(实测),而ADI手册要求<20mV——电源噪声会直接耦合到PLL输出。

第三步:“对症下药”——从硬件到软件的调整

针对以上问题,我做了三步优化:

1. 换“高精度晶振”,提升参考源质量

将26MHz TCXO替换为SiTime的SiT8921(相位噪声-130dBc/Hz@100kHz,温度稳定性±0.1ppm)。实测PLL输出相位噪声从-102dBc/Hz提升至-112dBc/Hz。

2. 调“环路滤波器”,抑制高频噪声

通过ADI提供的ADRV9008配置工具(ADRV9008 Configurator),将PLL环路滤波器带宽从100kHz调整为10kHz,并增大滤波器阶数(从2阶升3阶)。这相当于给PLL加了“低通滤波器”,滤除了高频噪声分量。

3. 优化“电源设计”,降低纹波干扰

在VDD_PLL引脚附近并联10μF陶瓷电容(低ESR)和0.1μF瓷片电容(高频旁路),并将电源路径从“主电源直接供电”改为“LDO稳压后供电”(LDO选ADI的ADP1715,压差150mV,噪声<10μVrms)。实测VDD_PLL纹波降至8mV,PLL相位噪声进一步改善至-118dBc/Hz。

实测结果:从“超标”到“优秀”的逆袭

调整后,我们在3.5GHz频段(n78)做了最终测试(环境温度25℃,输出功率23dBm):

| 指标 | 调整前 | 调整后 | 5G标准要求(3GPP TS 38.104) |

|---|---|---|---|

| 相位噪声(100kHz偏移) | -102dBc/Hz | -118dBc/Hz | ≤-110dBc/Hz |

| 邻道泄漏比(ACLR) | -55dBc | -68dBc | ≥-65dBc |

| 误码率(BER@10MHz) | 1.2×10⁻⁵ | 3.5×10⁻⁶ | ≤1×10⁻⁵ |

项目经理拍着评估板说:“这结果比客户要求的还好了1dB!下周演示稳了!”

经验总结:5G小基站射频前端的“避坑指南”

这次调试让我总结了三个关键经验,分享给同行:

1. 相位噪声要“全链路排查”,别只盯着芯片

ADRV9008虽集成度高,但相位噪声受晶振、电源、环路滤波器共同影响。调试时需用“替换法”逐一验证(如换晶振、改电源路径),避免“冤枉”芯片。

2. 参考时钟的“余量”很重要

5G小基站常工作在复杂环境(如温度-40℃~+85℃),晶振的温漂(±0.5ppm→±2ppm)会导致相位噪声恶化。选晶振时,建议留出至少5dB的余量(如标准要求-110dBc,选-120dBc的晶振)。

3. 电源设计“不能省”

PLL对电源噪声极其敏感,VDD_PLL纹波每增加10mV,相位噪声可能恶化2-3dB。小基站空间有限,可用“LDO+去耦电容”组合(如ADP1715+10μF+0.1μF),既节省空间又保证供电质量。

结语:ADRV9008的“隐藏技能”——让5G小基站“更稳、更远”

ADRV9008的强大不仅在于其集成的射频功能,更在于它对细节的把控(如灵活的PLL配置、低噪声电源设计)。通过这次调试,我深刻体会到:5G小基站的射频前端优化,是一场“从芯片到外围”的系统工程,而ADI的器件为工程师提供了“高起点”的解决方案。

如果你是5G小基站的研发工程师,还在为相位噪声头疼;如果你是采购,想找“高可靠+易调试”的射频收发器;甚至如果你是学生,想了解5G射频的前沿技术——ADRV9008都值得你深入研究。

互动话题:你在调试5G射频前端时,遇到过最头疼的相位噪声问题是什么?是晶振选型,还是电源噪声?评论区聊聊,关注者成科技/者成芯了解更多。

#5G基站#射频芯片#ADI#ADRV9008#者成科技#者成芯