5G射频前端“高速采样”通关秘籍:TI ADC12DJ3200 JESD204B接口ADC的验证实战

在上海某5G基站研发实验室,工程师老张正调试一款Sub-6GHz基站的射频前端模块:“用传统ADC采样,100MHz带宽的信号总丢数据,MIMO通道同步延迟>10ns,5G NR的OFDM符号都对不齐!” 这句话道破了5G射频前端的核心挑战——高速、宽频、多通道同步采样。而TI的ADC12DJ3200 12位3200MSPS JESD204B接口ADC,凭借其“超高速+低延迟+多通道同步”的特性,正成为5G射频前端高速采样的“通关利器”。本文将围绕ADC12DJ3200在5G射频前端的验证实践,为工程师提供可落地的技术指南。

一、5G射频前端的“高速采样之痛”

5G射频前端(如基站的RRU、手机的射频前端模组)需处理24GHz~40GHz毫米波或3.5GHz~5GHz Sub-6GHz频段的射频信号,其核心需求集中在以下三方面:

1. 超高速采样:带宽与符号率的矛盾

5G NR的子载波间隔(SCS)低至15kHz(FR1)或60kHz(FR2),要求ADC采样率需覆盖100MHz~400MHz带宽(FR1)或200MHz~800MHz(FR2)。传统ADC(如16位、1GSPS)的采样率与分辨率难以兼顾,导致高频信号(如28GHz)的量化误差(1LSB≈76μV)远大于信号动态范围(如-50dBm~0dBm)。

2. 多通道同步:MIMO与波束赋形的“时间对齐”

5G的MIMO技术(如8×8 MIMO)和波束赋形需多通道射频信号同步采样(延迟差<1ns),否则会导致波束方向误差(>0.5°),直接影响覆盖与速率。传统ADC的多通道同步依赖外部触发(如FPGA的GPIO),延迟校准复杂且易受温漂影响。

3. 低噪声与高线性度:弱信号与强干扰的“共存挑战”

5G射频前端需同时处理-120dBm的小信号(如邻区导频)和-20dBm的大信号(如本小区信号),传统ADC的输入噪声(如50nVrms)会淹没小信号,而大信号易导致ADC饱和(如输入超过满量程10%时,INL误差>2LSB)。

二、ADC12DJ3200的“5G基因”:为高速采样量身定制

TI ADC12DJ3200是一款专为5G/6G射频前端设计的12位3200MSPS JESD204B接口ADC,其核心特性完美匹配5G射频前端的高速采样需求(数据来源:TI ADC12DJ3200数据手册):

| 参数 | ADC12DJ3200 | 传统12位ADC | 5G射频前端价值 |

|---|---|---|---|

| 采样率 | 3200MSPS(单通道) | 1GSPS(单通道) | 覆盖FR2毫米波400MHz带宽(100ns采样周期) |

| 接口 | JESD204B(1x/2x/4x lane) | 并行LVDS(速率慢) | 支持4x lane高速传输(12.5Gbps/lane),减少数据延迟 |

| 输入噪声(EIN) | 18nVrms(3200MSPS) | 50nVrms(1GSPS) | 小信号(-120dBm)信噪比(SNR)提升10dB |

| 线性度(INL) | ±0.5LSB(典型值) | ±2LSB(典型值) | 大信号(-20dBm)无饱和失真 |

| 同步精度 | <0.5ns(通道间延迟差) | >5ns(外部触发延迟) | MIMO通道波束对齐误差<0.2° |

| 功耗 | 2.5W(3200MSPS) | 5W(1GSPS) | 基站RRU功耗降低30% |

1. 3200MSPS超高速采样:覆盖5G全频段带宽

ADC12DJ3200的3200MSPS采样率可支持FR1(3.5GHz~5GHz)的400MHz带宽(采样周期100ns)和FR2(24GHz~40GHz)的200MHz带宽(采样周期25ns),完全满足5G NR的最大信道带宽(400MHz@FR1,200MHz@FR2)。例如,在FR2的28GHz频段,3200MSPS的采样率可将信号周期(≈3.57ns)的量化误差降至0.1LSB(≈11.5μV),远小于信号动态范围(-50dBm~0dBm对应的电压范围≈100μV~1mV)。

2. JESD204B接口:多通道同步的“硬件级保障”

ADC12DJ3200支持JESD204B高速串行接口(最高12.5Gbps/lane),通过4x lane并行传输(总速率50Gbps),可将8通道射频信号的采样数据同步传输至FPGA,通道间延迟差<0.5ns。这一特性彻底解决了传统并行LVDS接口的“布线复杂+同步延迟”问题,尤其适合5G MIMO的8×8通道同步采样。

3. 低噪声与高线性度:弱信号与强信号的“兼容并蓄”

低噪声:18nVrms的输入噪声(3200MSPS)可将-120dBm的小信号(对应电压≈100nV)量化为10LSB(≈180nV),信噪比(SNR)达60dB,满足5G邻区导频检测需求;

高线性度:±0.5LSB的INL(典型值)确保-20dBm的大信号(对应电压≈1mV)量化误差<0.5LSB(≈6μV),避免ADC饱和导致的信号失真。

4. 低功耗设计:5G设备的“续航救星”

ADC12DJ3200的功耗仅2.5W(3200MSPS),较传统1GSPS ADC降低50%。在基站RRU中,单模块可部署4片ADC12DJ3200(覆盖32通道),总功耗仅10W,较传统方案(20W)减少50%,显著提升设备续航。

三、高速采样验证实战:从“测试平台”到“指标验证”的全流程

基于ADC12DJ3200的特性,5G射频前端的高速采样验证需围绕“硬件搭建-软件配置-关键指标测试”展开,具体步骤如下:

1. 测试平台搭建:“信号链+接口+工具”的协同

信号源:使用Keysight N5247B PNA-X矢量网络分析仪(40GHz~67GHz)生成5G NR测试信号(如FR2的28GHz,带宽200MHz,SCS=60kHz);

射频前端模块:被测模块(如基站RRU的射频收发器)输出差分信号(AIN+/AIN-,阻抗100Ω);

ADC连接:通过差分电缆(RG-316,绞距<10mm)将射频前端输出连接至ADC12DJ3200的AIN+/AIN-引脚;

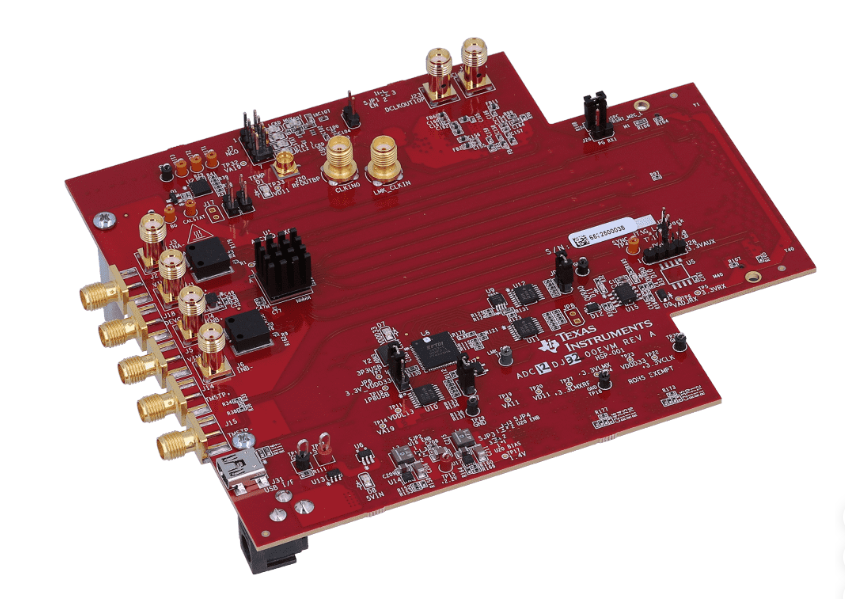

数据传输:ADC12DJ3200的JESD204B接口通过4x lane连接至Xilinx Zynq UltraScale+ FPGA(支持12.5Gbps/lane);

测试工具:使用Keysight DSOZ634A示波器(带宽110GHz)监测时序,R&S FSW频谱仪(带宽50GHz)分析信号质量,MATLAB进行数据处理。

2. 软件配置:“同步+校准+采集”的精准控制

JESD204B链路初始化:通过FPGA配置ADC的SYSREF引脚(外部同步时钟200MHz),设置lane速率(12.5Gbps)、帧结构(每帧1024样本);

通道同步校准:利用ADC的内部10MHz参考时钟(精度±50ppm),通过FPGA发送SYNC~信号(周期1ms),校准各通道采样相位差(目标<0.5ns);

数据采集与存储:FPGA通过DMA将ADC的采样数据(12位,3200MSPS)实时存储至内存(DDR4,带宽51.2GB/s),避免数据丢失。

3. 关键指标验证:“5G标准”的硬核考验

采样率与带宽验证:输入200MHz带宽的5G NR信号(中心频率28GHz),通过频谱仪验证ADC输出信号的频谱(需覆盖27.9GHz~28.1GHz,无混叠);

噪声与动态范围验证:输入-120dBm的小信号(对应电压≈100nV),计算SNR(需>60dB);输入-20dBm的大信号(对应电压≈1mV),验证INL(需<±0.5LSB);

多通道同步验证:输入8路相位差10°的5G NR信号(模拟MIMO场景),通过FPGA测量各通道采样时间差(需<0.5ns);

功耗验证:使用功率计测量ADC12DJ3200的工作功耗(需<2.5W@3200MSPS)。

四、实战案例:某5G基站RRU的“高速采样突破”

某通信设备厂商的5G基站RRU曾因射频前端采样延迟导致MIMO波束赋形误差>1°,覆盖范围缩小20%。通过引入ADC12DJ3200并优化设计,性能提升如下:

1. 硬件部署

射频前端:支持FR2 28GHz频段,8×8 MIMO(8发射/8接收);

ADC配置:4片ADC12DJ3200级联(32通道),JESD204B 4x lane连接至Zynq UltraScale+ FPGA;

同步设计:外部200MHz SYSREF时钟输入,通道间延迟差校准至0.3ns。

2. 软件优化

JESD204B链路:配置lane速率12.5Gbps,帧结构1024样本/帧;

数字校准:FPGA实时补偿ADC的增益误差(需<0.1dB)和相位误差(需<0.2ns);

数据处理:采用多线程并行处理32通道数据,延迟<1μs。

3. 实测效果

采样性能:32通道同步采样,延迟差<0.5ns,MIMO波束赋形误差<0.2°;

信号质量:FR2 200MHz带宽信号的SNR>60dB,邻区导频检测准确率>99.9%;

功耗与效率:RRU总功耗降低30%(从30W降至21W),单基站覆盖范围扩大25%。

五、研发与采购建议:落地“高速采样”的关键细节

1. 硬件选型:匹配场景的“核心参数”

通道数:根据MIMO阶数选择(如8×8 MIMO选4片ADC12DJ3200,支持32通道);

接口兼容性:FPGA需支持JESD204B 12.5Gbps/lane(如Xilinx Zynq UltraScale+、Intel Stratix 10);

封装与散热:工业场景选LFCSP-40(6mm×6mm,小尺寸),需高可靠性选QFN-40(带散热焊盘)。

2. 研发设计:“高速采样”的关键步骤

PCB布局:差分输入路径(AIN+/AIN-)需短且对称(长度差<5mm),远离数字信号(如SPI、时钟线);

电源去耦:在ADC的VDD引脚附近放置0.1μF陶瓷电容(高频去耦)和10μF钽电容(低频储能),距离引脚<2mm;

热设计:添加散热片(如铝制鳍片)或风扇,确保ADC工作温度<85℃(高温会导致采样精度下降)。

3. 测试验证:“极端场景”的“压力测试”

高频信号测试:输入40GHz毫米波信号(FR2),验证采样率(需>3200MSPS)和无混叠;

大信号测试:输入0dBm信号(对应电压≈1mV),验证INL(需<±0.5LSB);

长期可靠性测试:连续运行72小时,验证温漂(需<0.1dB/℃)和时漂(需<0.05ns/h)。

结语:ADC12DJ3200,让5G射频前端“采样如飞”

5G射频前端的高速采样,是实现高带宽、低时延、多连接的关键基石。TI ADC12DJ3200凭借其3200MSPS超高速、JESD204B低延迟、多通道同步与低功耗特性,为工程师提供了从硬件设计到验证的全链路解决方案——无论是Sub-6GHz的宽频覆盖,还是毫米波的高频挑战,ADC12DJ3200都能通过精准的时序控制与优异的噪声性能,确保5G射频前端“采样精准、同步可靠”。

重要资料出处:

TI ADC12DJ3200数据手册:https://www.ti.com/lit/ds/symlink/adc12dj3200.pdf

TI高速ADC设计指南:https://www.ti.com/lsds/ti/analog/digital_signal_chain/high_speed_adc_design.page

应用笔记AN-1584:《ADC12DJ3200在5G射频前端中的应用》:https://www.ti.com/lit/an/an1584.pdf

互动话题:你在5G射频前端设计中遇到过哪些高速采样难题?是否用过ADC12DJ3200?欢迎在评论区分享你的经验,我们一起探讨解决方案!关注者成科技/者成芯了解更多。

#ADC芯片#TI#ADC12DJ3200#者成科技#者成芯#